The SiFive is SoC compatible with all applicable RISC-V standards, So what is RICS-V exactly ? Umm, RICS-V is an open standard instruction set architecture (ISA) based on reduced instruction set computer (RISC) principles and using it software communicate to processors. Read More about RICS-V.

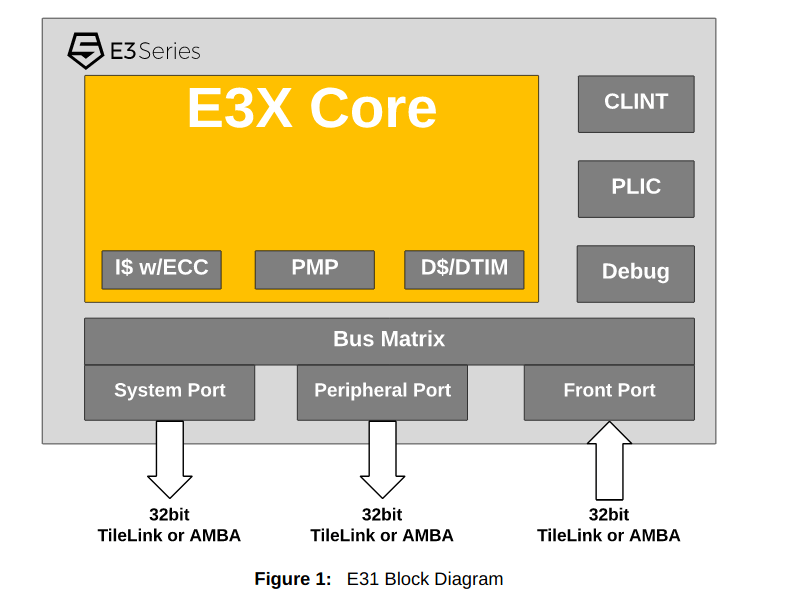

It is built around the E31 Core and fabricated in the TSMC CL018G 180nm process.

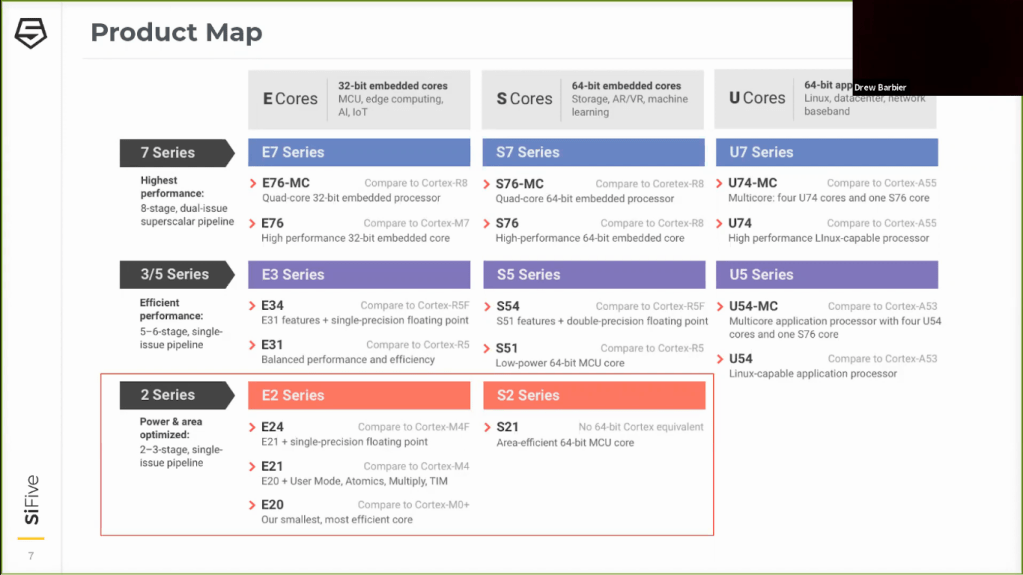

I hope you get idea what is SiFive and what architecture it follow, how it is built and other SiFive profucts.So lets dig out how is it made up.

- E31 core

- I/O peripherals

- 8KiB OTP memory

- 8 KiB of mask ROM

- clock generation

- Quad-SPI flash controller

- Always-on (AON) block

Some More Details about RISC-V E31Core

It has 32-bit E3 RISC‑V core and The E3 core is configured to support the RV32I base ISA, as well as standard Multiply (M),Atomic (A), and Compressed (C) RISC‑V extensions (RV32IMAC). The Pipeline execution has five stages. 1.Fetch 2. Decode 3.Execute 4.Data memory access 5. Register write-back.

- Introduction to ARM Architecture and Its Impact

- Understanding C++ Object Model: Virtual Table and Virtual Pointer

- How to create a thread and execute it on specific CPU Core

- Real Time Logging for Embedded Systems and IoT

- Difference between structure and union

- Constant Pointer, Pointer to constant and Constant pointer to constant

- Volatile in c and Compiler optimization

- Storage classes in C

Tnxx,Quite good, waiting for next..

LikeLiked by 1 person